ARM Processor (Verilog)

Written on June 20th, 2020 by Dan Peluso

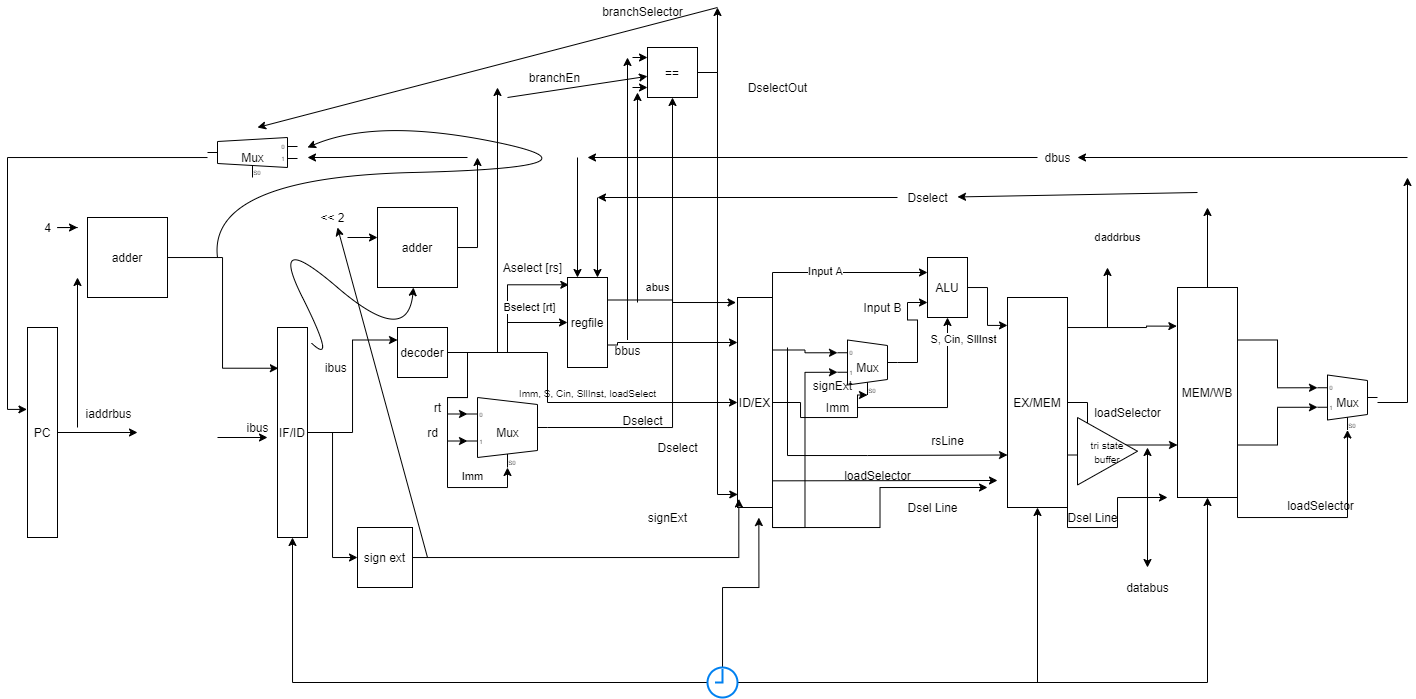

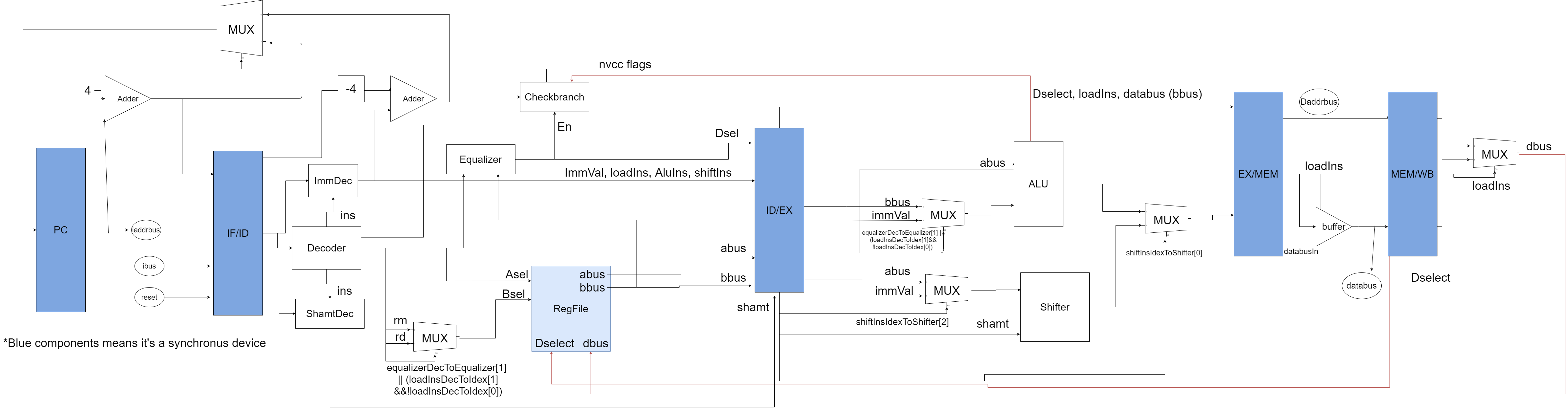

The code below is the top module for a CPU which uses the ARMv8 instruction set. This processor is capable of utilizing the following instructions:

For this particular model, the instruction set is given as an array of instructions, and given the 4-cycle delay should produce the correct values in the destination register. The memory system was not modeled in this implementation, but to simulate it I made a tristate buffer to use the memory ‘Databus’ as both an input and output.

I calculated the IPC to be ~.67, which I explain below:

For easier reading, I put all the submodules directly below the top module.

Skills

- Verilog

- ARMv8

- Vivado

- Digital Hardware Design

Feel free to share!